更新时间:2025-12-20

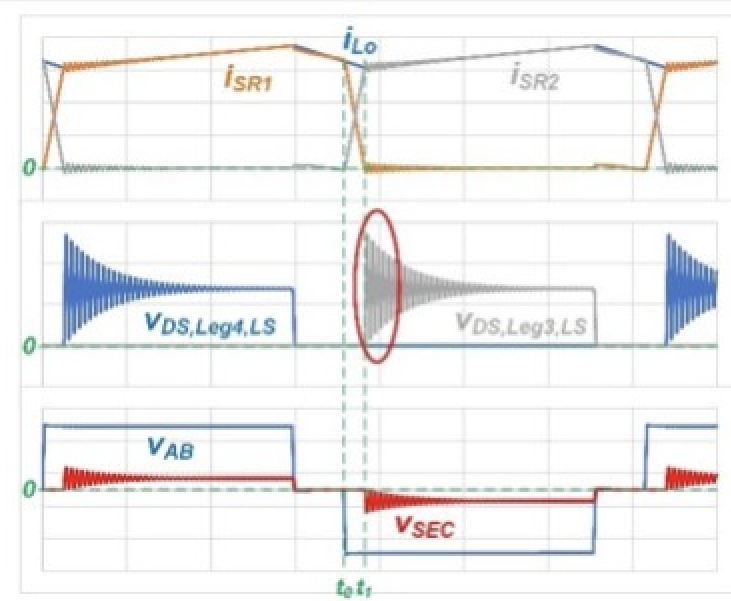

以上的应用中很受欢迎,因为它可在输入开关上实现软开关,从而提高转换器效率。虽然开关损耗大大降低,但输出整流器上仍会出现高压应力,因为其寄生电容会与变压器

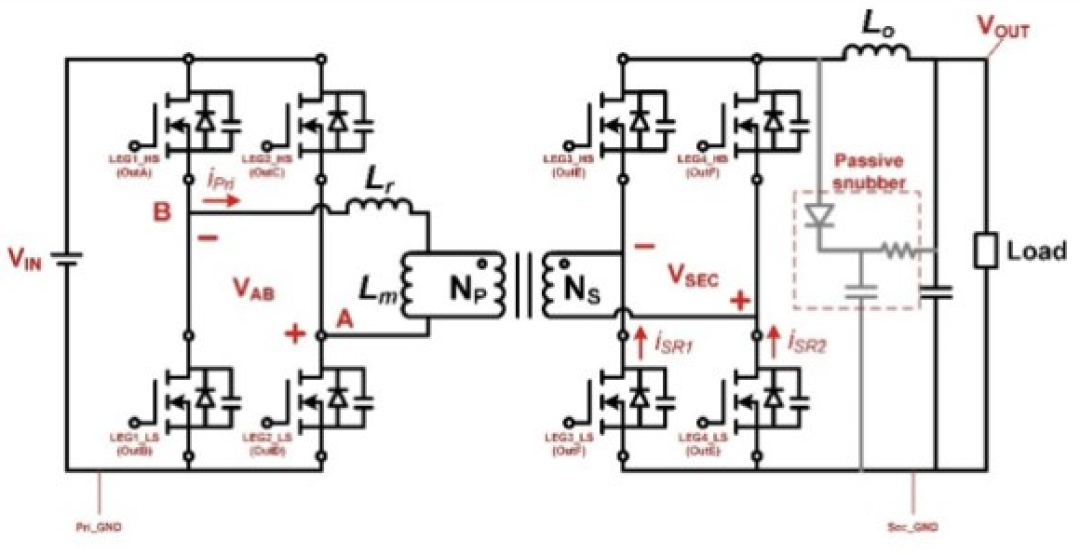

传统上,要限制输出整流器上的最大电压应力,需要无源缓冲器,例如电阻器-电容器-二极管 (RCD) 缓冲器,但使用无源缓冲器将消耗功率,从而导致效率损失。

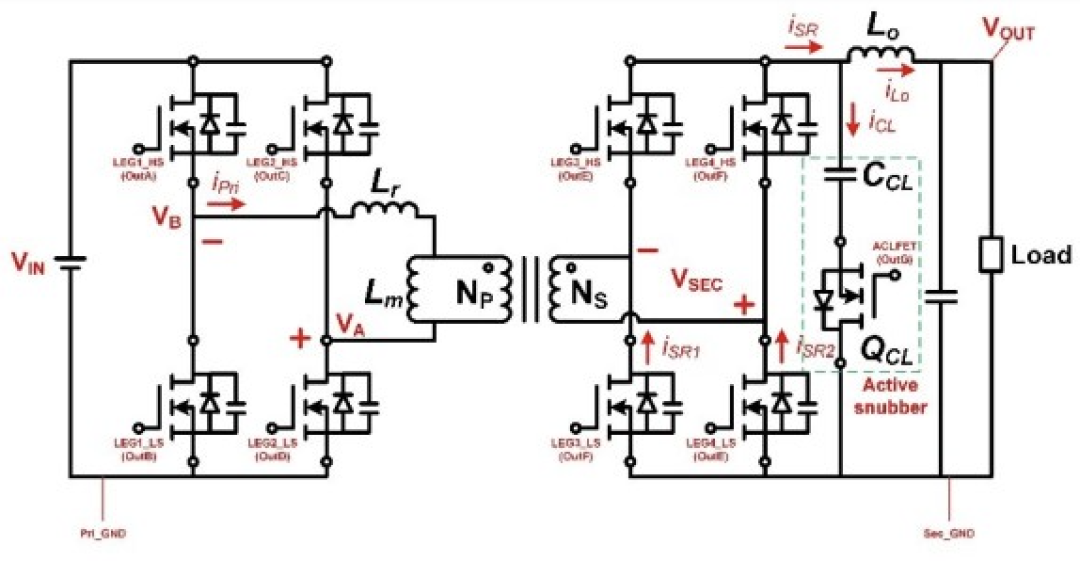

或者,您可以应用有源缓冲器来钳制整流器电压应力,而不消耗缓冲器电路中的任何功率(假定存在理想开关)。图 2 显示由 (CCL) 和MOSFET(QCL) 形成的有源钳位桥臂 (ACL)插入到输出电感器之前。当输出绕组电压变为非零时,能量将从初级绕组转移到次级绕组,以便将输出电感器通电,还会通过QCL体二极管传导电流以对 CCL充电,即使 QCL未导通也是如此。您可以在 QCL体二极管已传导电流后将其导通,以在 QCL上确保零电压开关 (ZVS)。

图 2 对于具有有源钳位和波形的 PSFB 功率级,与无源缓冲器不同,有源缓冲器不会消耗功率电阻器上的振铃能量,而是作为无损缓冲器在 LC 谐振回路中实现能量循环。

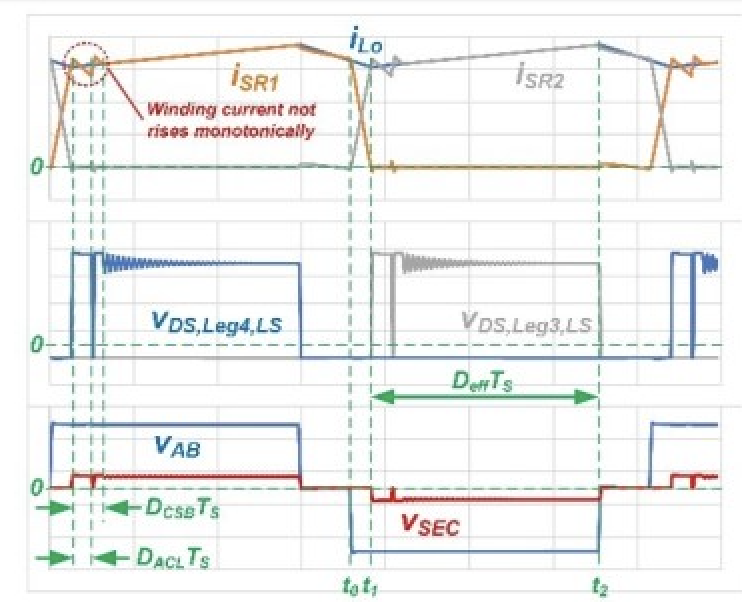

请务必在有源钳位 MOSFET (ICL) 极性变化之前导通 QCL,以便在有效占空比 (DeffTS) 开始时完成 CCL上的电流秒平衡。换句话说,QCL只需导通足够长时间,即可使有源缓冲器的电流秒平衡按照预期发挥作用,从而将输出整流器电压钳位到 CCL电压 (VCL)。换句话说,QCL不需要在整个DeffTS期间内导通,只需在相对较短的时间段内导通。因此,QCL可以有一个固定的导通时间,即 QCL导通时间(DACLTS)是常量,同时保持 DeffTS始终大于电流秒平衡 (DCSBTS) 完成的持续时间。

这种方法解决了使用有源缓冲器时的一项挑战,因为变压器绕组电流不会单调上升,而如果使用峰值电流模式控制,这会是一个问题。这是因为有源缓冲电容器的能量还会参与使输出电感器通电,而不仅仅依赖于初级侧的能量传送。由于DeffTS大于 DCSBTS,因此当变压器电流单调上升时,可能进行峰值电流检测。由于具有较大 Deff的 PSFB 有望实现高效率,因此您可以将 PSFB 设计为在中高负载条件下具有较大 Deff,此时Deff DCSB。在轻负载条件下,转换器应该在不连续导通模式下运行,此时Deff将小于连续导通模式下的 Deff(在相同的输入/输出电压条件下)。为了使 DeffTS即使在轻负载条件下也大于 DCSBTS,您可以使用降频控制或突发模式控制。

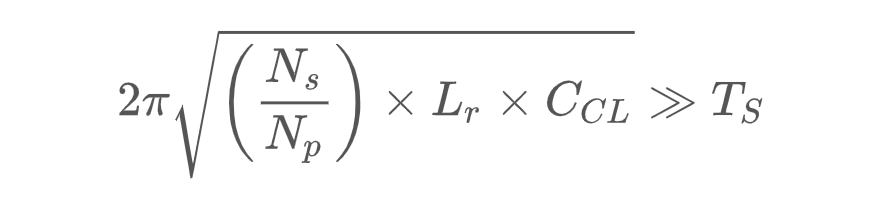

因为 CCL纹波电压会影响输出整流器上的总电压应力,因此您必须选择足够大的 CCL以实现低电容器纹波电压。您还必须选择 CCL,以便由 Lr和 CCL形成的电感器-电容器 (LC) 谐振周期远长于由公式 1 表示的开关周期:

使用有源缓冲器时,整流器电压应力将钳制在VINNS/NP左右,这大约是没有任何钳位电路时电压应力的一半。与无源缓冲器不同,有源缓冲器不会消耗功率电阻器上的振铃能量,而是作为无损缓冲器在 LC 谐振回路中循环能量。因此,在相同规格下,与使用无源缓冲器的 PSFB 相比,预计使用有源缓冲器的 PSFB 转换器效率更高。

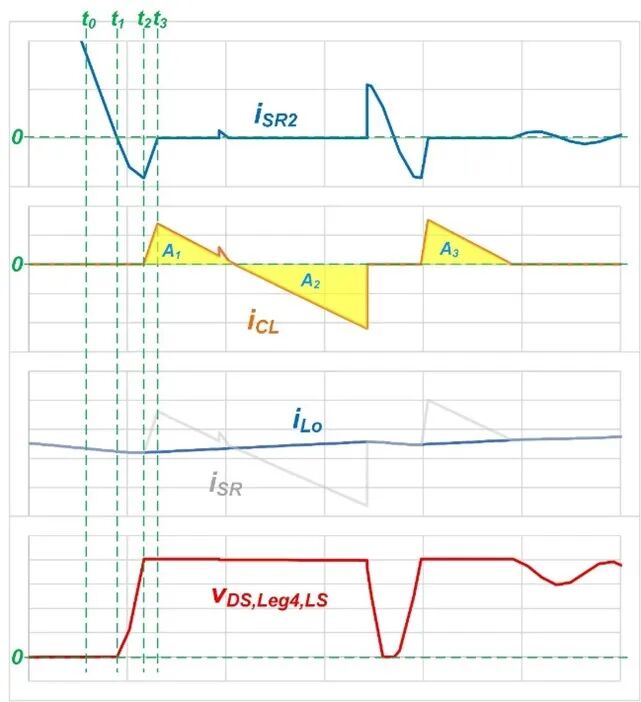

要了解决定ACL电流值的因素,您需要计算流经 ACL 本身的电流。图 3 展示了 ACL 导通周期的波形。

假定VCL为常量且 Lm= ∞,则公式 2 在漏源电压上升时推算输出整流器 (iSR2) 一侧的电流,如下所示:

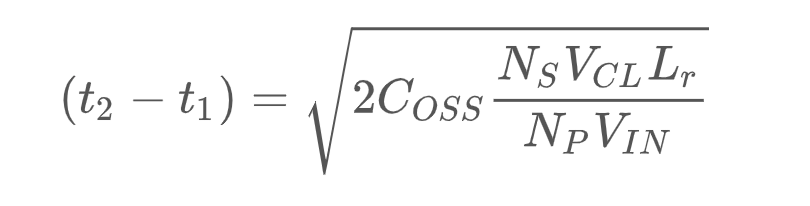

通过假定iSR2电流以恒定速率减小,公式 3 可推算 t2-t1的持续时间,如下所示:

由于 CCL需要保持电流秒平衡,因此面积 A1 和 A3 之和将等于面积 A2。通过所有这些信息,可以计算iCL的均方根 (RMS) 值。如公式 3 所示,同步整流器 (SR) 输出电容 (COSS) 控制 ACL 上的峰值电流。如果您选择较低 CossSR FET,则 ACL RMS 电流会更低,从而有助于提高转换器效率。

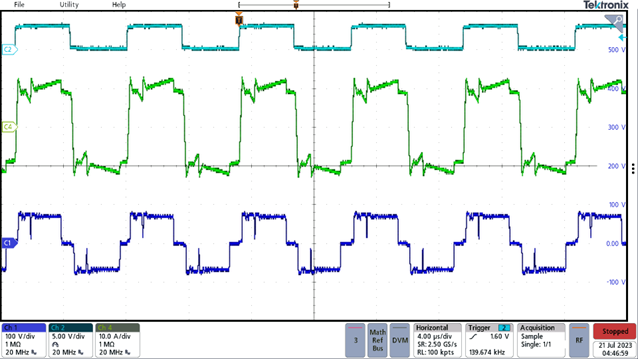

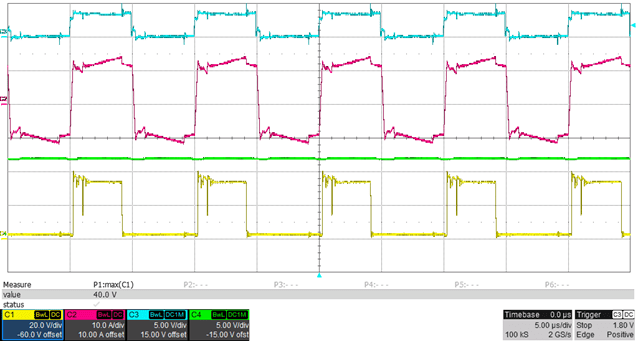

图 4 显示了德州仪器 (TI) 采用有源钳位的54V、3kW相移全桥参考设计的波形。该参考设计是一款400V 输入、54V 输出、3kW PSFB转换器,采用通过TIC2000™ 微控制器实现的有源钳位。在此设计中,变压器匝数比为Np:Ns = 16:3。当 ACL FET 在输出电感器通电期间仅导通300ns时,即使在3kW负载下,输出整流器电压应力(图 4 中的 Ch1)也限制为80V。较低的电压应力使得可以选用耐压等级较低、性能指标更优的 SR FET,从而进一步提升 PSFB 的效率。

这种控制方法不限于具有一个 ACL 的全桥整流器;您也可以将其应用于具有其他类型整流器的有源缓冲器,例如倍流器或中心抽头整流器。TI推出的采用有源钳位、功率密度大于270W/in3的 3kW 相移全桥参考设计包含带有源钳位的400V 输入、12V 输出、3kW PSFB 转换器,其中次级侧使用中心抽头整流器。即使在3kW负载条件下,输出整流器应力(在 图 5 中为 Ch1)也限制为40V。

在 PSFB 转换器中实现有源缓冲器可显著降低输出整流器上的最大电压应力。电压应力的降低使得可以选用耐压更低的 SR FET,从而实现更优的性能指标。虽然有源钳位会在实现峰值电流模式控制方面带来挑战,但只要实现方式得当,依然可以实现有源钳位与峰值电流模式控制协同作用。与传统 PSFB 实现方式相比,这种组合可提高功率密度和效率。